8080 内部ビット可視化シミュレータ – ALU の動きを LED で体感

これは何?

8080 内部ビット可視化シミュレータ は、インテル 8080 CPU の ALU と主要レジスタを LED で丸ごと見える化 した学習ボードです。 1 クロックごとに “Accumulator”、“演算結果”、“フラグ” などが即座に点灯し、8 bit CPU が今何をしているか を手に取るように追えます。

基板サイズは約 100 mm 角。USB 給電のみで動作し、あらかじめ書き込んだプログラムのステップ実行が可能です。6 月の NT 金沢 2025 と 9 月の NT 東京 2025 に出展し、多くの方に実際に体験していただきました。

動機

- 「レジスタやフラグって結局 0/1 のデータを記録しているだけでしょ?」を LED の点滅 で体験してもらいたい

- 黒い IC の中身を覗けないもどかしさを解消し、CPU アーキテクチャを"感覚で"理解する教材 に

- 8080 は Z80・8086 系列のルーツ。8 bit マイコンを学ぶ入口 として最適

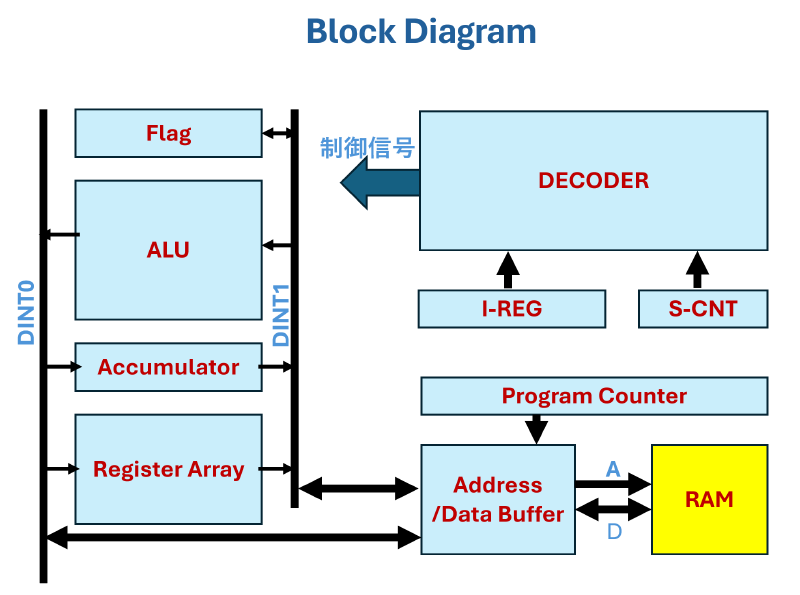

CPUシステム構成

| ブロック | 基板上の表示 | 役割 |

|---|---|---|

| ALU | 8 × LED | 加算・論理演算結果をリアルタイム表示 |

| Accumulator | 8 × LED | A レジスタ内容 |

| Register‑Array | 2 × LED | B/C/D/E… 汎用レジスタのenableとload enable |

| Flag | 5 × LED | S/Z/P/HC/C 各フラグ |

| Program Counter | 2 × 7seg | 実行中アドレスを 16 進表示 |

| Decoder | - | 命令をデコード |

上記ブロックは PPT のブロック図にほぼ対応しています。 基板自体は “表示専用” で、CPU の演算は ESP32 上で動作する 8080 シミュレータが担当。Verilog で記述した 8080 CPU を Yosys の CXXRTL で C++ にトランスコンパイルし、ESP32 で実行。出力信号だけを LED に配線しているため、配線は単純で作りやすくなっています。

使い方デモ

スライドに掲載した 11 ステップのデモプログラムでは、ロード/算術/論理/ローテート/メモリアクセスを一通り実行し、各ビットの遷移を観察できます。

MOV B,AAH– B レジスタに AA をロードMOV A,55H– A に 55 をロードADD B– A と B を加算(A=FF)ADI 01H– A に 1 を加算(A=00, CY=1)ORA B– A と B の OR を A に格納(A=AA)RAL– A を左ローテート(A=55)XRI FFH– A と FF の XOR(A=AA)ANI 3FH– A と 3F の AND(A=2A)STA 1000H– A を RAM アドレス 1000H に保存ANI 00H– A と 00 の AND(A=00)LDA 1000H– RAM アドレス 1000H から A に読み込み(A=2A)

LED を見ているだけで キャリーの伝播 や AND/OR のビットマスク がわかり、初学者にとって 直感的な理解 につながりました。

技術

本システムの最大の特徴は、Verilog で記述した 8080 CPU を ESP32 上でソフトウェアとして実行 していることです。Yosys の CXXRTL 機能を使用して Verilog コードを C++ に変換し、マイクロコントローラー上で動作させています。

詳細な実装方法については「Verilog を C++に変換して ESP32 で動かす」をご覧ください。

114個のLEDは、36本対応のLEDドライバIC(IS31FL3236)を4つ使って制御。

展示

NT 金沢 2025(2025年6月)

初回出展では多くの反響をいただきました:

- 小学生から古のエンジニアまで 幅広く立ち止まってくれ、「8080 って 50 年前の石でしょ!?」「バス線が光るの最高!」と大盛り上がり

- 「命令追加できますか?」→ Verilog から生成されたソフトウェア実装なので今後のアップデートでほぼ無制限

- 「Z80 版も見たい」→ 次回作候補です

NT 東京 2025(2025年9月)

東京での展示では、さらに多くの技術者や教育関係者の方々と交流することができました:

来場者の反応:

- 「CPU の動きが目で見えるのが面白い」

- 「教育に使えそう」

- 「レトロコンピュータへの興味が湧いた」

ライトニングトークでの発表

NT 東京 2025 では、ライトニングトークでも本プロジェクトを紹介しました。8 ビットから始めて最終的に Z80 全体へ展開するロードマップや、学習・教育での活用可能性について述べました。

発表資料: NT東京2025 ライトニングトーク資料 (PDF)

詳細なレポートは「NT東京 2025参加レポート」をご覧ください。

今後の課題

- 8080 全命令の実装

- 現状は ALU と主要レジスタのみ。条件分岐対応など全命令の実装を進めたい。

- マイクロステップ表示

- フェッチ/デコード/実行のサブサイクル用のLEDを追加しより具体的にDecoder部を表示する。

- レジスタやメモリの可視化

- 別基板を追加し、より多くのレジスタ・メモリ情報を表示できるように拡張。

- プログラムの書き換えを容易に

- 現状プログラムはハードコードされているが、外部のエディタから書き換えられるようなしくみを構築する。

- 教材パッケージ化

- 組立キット+ワークブック+オンライン IDE を整備し、高校・高専の教材として展開。

おわりに

CPU の内部はブラックボックスと言われがちですが、1 本 1 本の信号線とゲートこそがコンピュータの本質。 本ボードは「光るだけ」で終わらず、“見えるから分かる → 分かったら試したくなる” という学びの連鎖を引き起こします。

次は Z80 や 6502 でもっと派手に光らせたい!

関連記事

- NT東京 2025参加レポート - 8080 Simulator & Smart Knob LHD展示記録9月 10

イベント概要 2025 年の NT 東京に参加し、「8080 内部ビット可視化シミュレータ」と「Smart Knob LHD」の 2 作品を出展しました。多くの方に実際に触っていただき、貴重なフィードバックをいただくことができました。 出展 …

VerilogをC++に変換してESP32で動かす9月 9

VerilogをC++に変換してESP32で動かす9月 9背景 現在、8080 simulatorプロジェクトにて、Intel 8080 CPUの回路をVerilogで記述し、それをESP32上で実行して内部状態を可視化するシステムを開発しています。このプロジェクトでは、本来FPGAやASICで動 …

NT東京 2025参加のお知らせ9月 5

NT東京 2025参加のお知らせ9月 5直前のご案内になりますが、NT 東京 2025に出展します。お時間が合う方はぜひお立ち寄りください! 出展情報 日時:2025 年 9 月 6 日(土)・7 日(日) ブース:E4「DDD」 ステージ発表:9 月 6 日( …