1分

初めての半導体設計・製造体験!ISHI会インバータ回路ハンズオン参加レポート

はじめに

2025 年 9 月 13 日、ISHI 会主催の「初めての半導体設計・製造体験!一日で作るインバータ回路ハンズオン」に参加ました。このイベントは、半導体設計初心者でも一日で回路設計から、シミュレーション、レイアウトまでを体験できる貴重な機会でした。

ISHI 会と OpenMPW について

ISHI 会(Inter-linked Society on Homemade IC Kai)は、半導体のオープンソースムーブメントを推進するコミュニティです。Google が Efabless 社に出資して生まれた OpenMPW(Open Multi Project Wafer)プログラムを活用し、従来は専門家だけが利用可能だった半導体製造を誰もが体験できる環境を提供しています。

インバータ回路とは

今回設計したのは、デジタル回路の基本要素であるインバータ(NOT ゲート)です。入力信号を反転させる最もシンプルな論理回路で、半導体設計における「Hello World」的な存在です。

実際の設計体験

環境構築

まずはオープンソースの EDA ツール環境をセットアップ。コンパイルとインストールを自動で行ってくれるスクリプトをあらかじめ用意してくださっています。うまく行けば、それを実行するだけで終わります。

MAC でのコンパイルはバージョンのコンパティビリティの問題から難易度が高く、結局 windows の WSL2 上の Ubuntu 内に環境を構築しました。

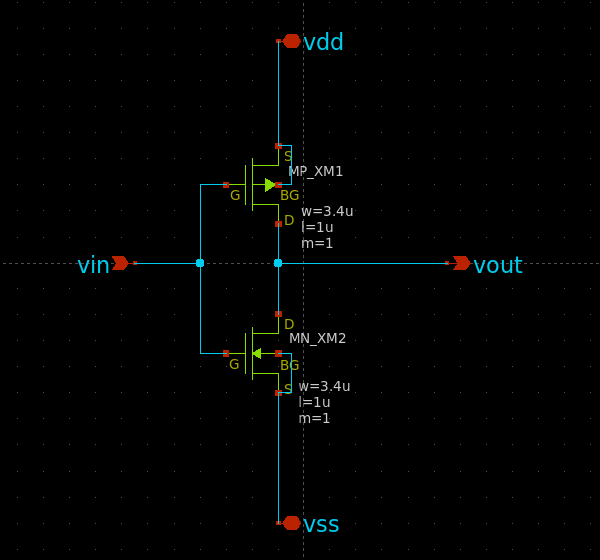

回路設計

シンプルなインバータ回路です。CMOS の基礎になる要素です。xschem を使用して回路を書きました。

シミュレーション

設計した回路の動作確認を ngspice を使用して実施しました。2 つの異なるシミュレーションを行い、回路の性能を詳細に評価しました。

1. 回路の動作確認(DC 解析)

インバータ回路が正しく機能するかを確認するため、入出力特性を解析しました。具体的には以下を確認しました。

- 入力が高電圧(VDD、論理 1)のときに出力が低電圧(VSS、論理 0)になることを確認

- 入力が低電圧(VSS、論理 0)のときに出力が高電圧(VDD、論理 1)になることを確認

- 電流量を確認

2. 過渡状態の確認(Transient 解析)

コンデンサを擬似的な負荷として追加して、回路が入力信号の変化にどのように応答するかを時間的に解析しました。

- 立ち上がり時間(Rise Time)

- 立ち下がり時間(Fall Time)

- 遅延時間(Propagation Delay)

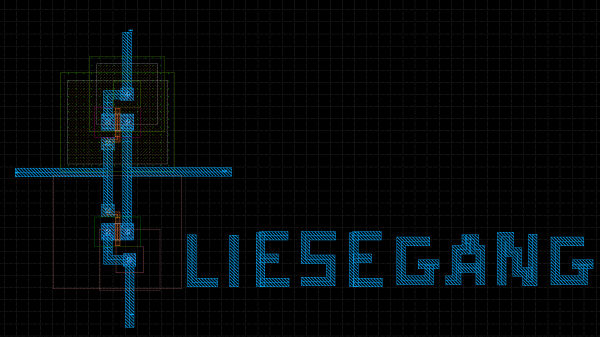

レイアウト設計

klayout を用いて行いました。

最も印象的だったのがこの工程でした。回路図からレイアウトがある程度自動生成されると期待していましたが、実際には以下のような工程が必要でした。

1. 素子の配置

- MOSFET などの基本素子は、PCell(Parameterized Cell)という形でライブラリ化されています。これは、パラメータ(素子の長さや幅、コンタクトの有無など)を指定すると、プロシージャルに素子を制し得してくれるコンポーネントです。

- 今回はIP62というオープンソースライブラリを使用しました

- ソフトウェアによるガイドなしに、一から必要な MOSFET の PCell を選び、手動で配置し、パラメータを調整します

2. 配線の接続

- 一つ一つの配線をガイドなしに手動で接続しました

3. DRC(Design Rule Check)

- 設計ルールチェックをクリアするための調整を行いました

- PCB 設計と異なり、半導体設計ではクリアランス違反があると製造不可能になるため、非常にシビアな修正が必要です

- 記念に名前の文字をお絵かきしましたが、DRC 違反のため修正が必要でした…

4. LVS(Layout Versus Schematic)

- レイアウトと回路図の整合性を検証しました

- xschem で作成したネットリストを使用して接続を確認します

- ここで初めて回路図の情報と照合します(それまでは回路図による設計支援はありません)

成果物

イベントの成果として以下のファイルを作成しました:

- my_inv_gate.sch: 回路図ファイル

- my_inv_gate.gds: レイアウトファイル(GDSII 形式)

これらのファイルはGitHub リポジトリで公開しています。

学んだこと・感じたこと

設計支援が少ない

今回使用したオープンソースツールでは、設計支援機能が想像以上に少ないことに驚きました。

PCB 設計との比較:

- PCB 設計:部品のフットプリントが自動選択され、配線にもガイドが表示される

- 半導体設計:素子の配置から配線まで、設計支援がほとんどない

特にレイアウト段階では、製造可能性を考慮した物理的な制約が多いにも関わらず、それらをクリアするための支援機能が限られていました。

今後への興味

この体験を通じて以下への興味が湧きました:

- 最新の商用 EDA ツールではどの程度まで自動化が進んでいるのか

- Verilog から論理合成された大規模回路のレイアウト手法

- 8bit CPU といった複雑な回路の設計

- アナログ回路で使用するキャパシタ、抵抗、インダクタなどの受動素子の設計

まとめ

このワークショップを通じて半導体設計の奥深さと面白さを実感しました。オープンソースの力によって、従来は専門家だけのものだった半導体設計が身近になったことは素晴らしいことです。

半年後には OpenMPW プログラムを通じて実際のチップが完成し、測定会も開催される予定です。自分が設計した回路がどのくらいシミュレーションに忠実に動作するのか、今から非常に楽しみです。

もしこの記事を読んで「自分も半導体設計に挑戦してみたい!」と思った方は、ぜひ次回の ISHI 会ワークショップや勉強会に参加してみてください。初心者でも歓迎されており、実際に手を動かしながら学べる貴重な機会です。質問や相談も気軽にできる雰囲気で、誰でも挫折せずに半導体の設計を楽しく体験で切ると思います。

関連リンク

補足コラム:商用 EDA ツールではどこまで自動化されているのか?

今回のワークショップではオープンソースの EDA を用いたため、「設計支援が少ない」という印象を持ちました。しかし、Cadence、Synopsys、Siemens などが提供する商用 EDA ツールでは、以下のように高度な自動化・支援機能が備わっているらしいです。

回路図からレイアウトへ(Schematic Driven Layout)

- 回路図上で定義した素子や接続情報をもとに、配置や配線が自動生成

- 特にアナログ設計では「左右対称配置」「等長配線」など、手作業だと大変な制約を与えて半自動で実現可能

編集中に走るサインオフ級の DRC / LVS

- Siemens Calibre RealTime や Synopsys IC Validator などを使えば、レイアウト編集中に即座に DRC(設計ルールチェック)違反を検出

- LVS(回路図とレイアウトの照合)もワンボタンで確認でき、エラー箇所を GUI 上で追跡(これはオープンソースツールでもある程度できてたかも)

電源・信号品質の同時解析

- Cadence Voltus や Synopsys RedHawk-SC を使えば、P&R(配置配線)途中でも IR ドロップや EM(エレクトロマイグレーション)を解析

- STA(タイミング解析)とも連携し、配線やバッファを自動修正

自動フィル・多重パターニング対応

- 配線後の金属フィル挿入や、先端ノードに必須の多重パターニング対応も自動化

AI による設計探索

- Synopsys DSO.ai や Cadence Cerebrus は機械学習を使い、PPA(性能・電力・面積)のトレードオフ探索を自動化

- 人間が数週間かけて試行錯誤する代わりに、AI がクラウド上で何千もの実験を回し、よりよい解を提案